- Visual studio code logo 640x480 how to#

- Visual studio code logo 640x480 install#

- Visual studio code logo 640x480 full#

See the extension's documentation for the full, up-to-date list of supported features. This article describes only a subset of the features the Go extension provides.

Visual studio code logo 640x480 how to#

Watch "Getting started with VS Code Go" for an explanation of how to build your first Go application using VS Code Go.

Visual studio code logo 640x480 install#

You can install the Go extension from the VS Code Marketplace.

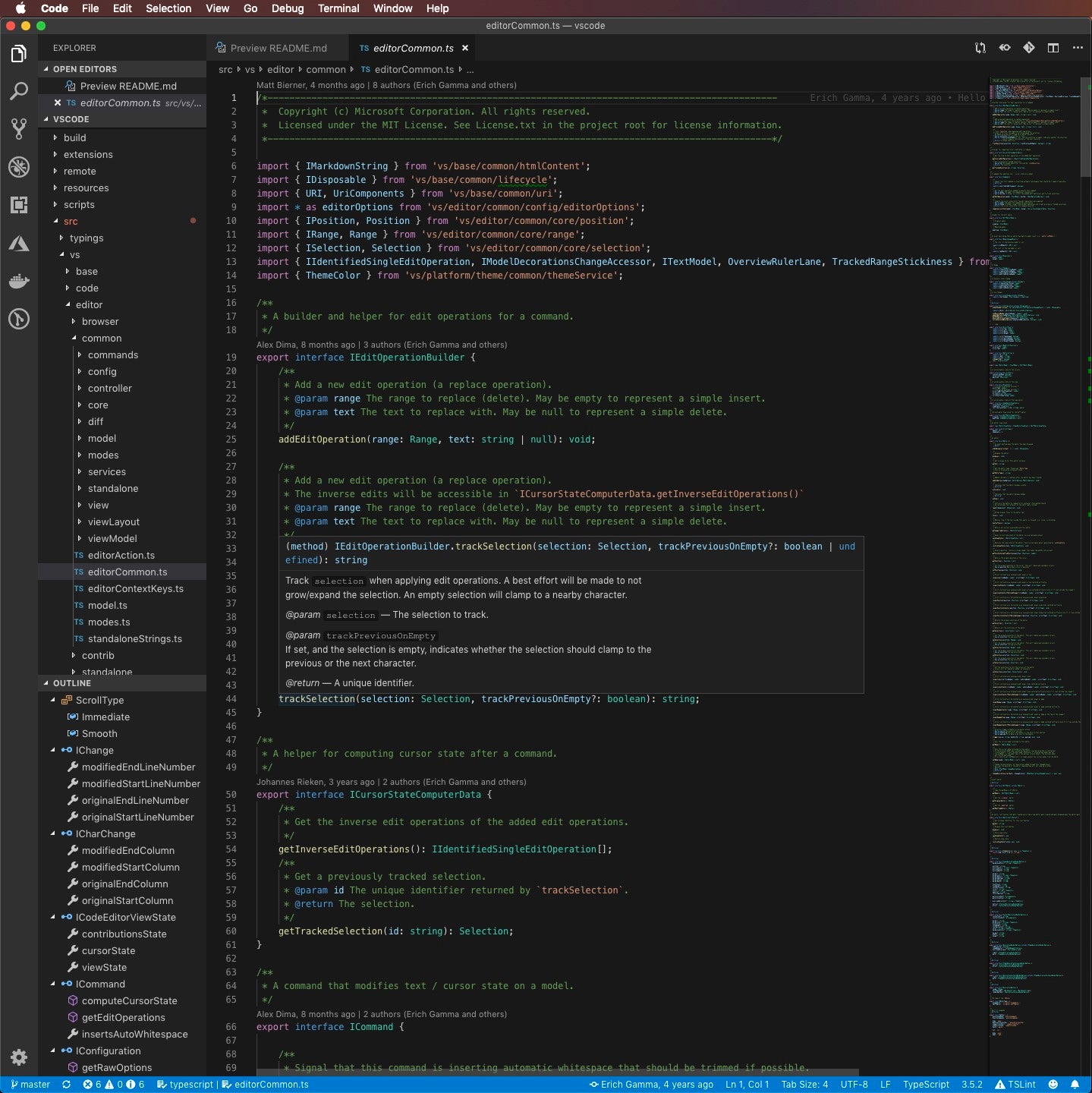

Using the Go extension for Visual Studio Code, you get features like IntelliSense, code navigation, symbol search, testing, debugging, and many more that will help you in Go development.

Visual studio code logo 640x480 full#

Exploiting full features of this architecture, we have developed schemes for an efficient parallel Provides a peak computation power of 96 GFLOPS while consuming only 9 Watts, making it an excellent candidate for embeddedĬomputing applications. With two cores, each with 96 Processing Elements, this SIMD architecture Massively parallel SIMD architecture, the CSX700. In this paper, we present faster than real-time implementation of a class of dense stereo vision algorithms on a low-power We show that, by designing appropriate efficient parallel algorithms, this highly parallel SIMD architecture can represent an excellent candidate for space-borne applications wherein low-power, light weight, high performance computation is a major requirement. Compared with GPGPUs, we achieve similar (and for some cases better) computational performance but with a significantly better relative performance per watt. This comparison cealrly demonstrates that we achieve a much better absolute computational performance than ASICs and FPGAs, with a better relative performance per watt. We also compare our results, when applicable, with similar implementations on ASIC, FPGAs, and GPGPUs. Our results indicate that this SIMD architecture is indeed a good candidate for achieving low-power supercomputing capability, as well as a rather satisfactory degree of flexibility for implementing various applications. We present parallel implementation results for four classes of image processing applications: feature detection (Harris Corner Detector), stereo vision (a class of SSD like algorithms), model estimation (RANSAC), and object detection (based on Histogram of Oriented Gradient, HOG) on the CSX SIMD architecture. In this paper, we present and discuss high performance implementation of a wide class of image processing applications on a low-power massively parallel SIMD architecture, the ClearSpeed CSX700.

0 kommentar(er)

0 kommentar(er)